Celestial AI Combines HBM & DDR5 Memory To Lower Power Consumption By 90%, Could Be Used By AMD In Next-Gen Chiplets

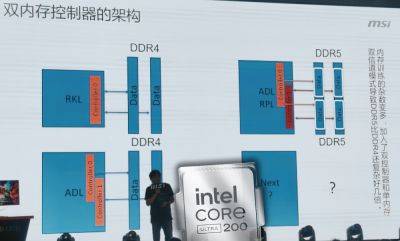

Startup, Celestial AI, has developed a new interconnect solution that utilizes DDR5 & HBM memory to increase the efficiency of chiplets with AMD possibly being among the first to use such a design.

Celestial AI Plans On Breaking The Barriers Associated With Traditional Interconnects, Courtesy of Silicon Photonics, Which Combine HBM And DDR5 Memory

Like semiconductors, generational evolution has become more than necessary for the AI industry, whether in the form of advancements within the hardware segment or the interconnect methods.

Related Story AMD & Vindral Demo 8K 10-bit HDR Live Streaming With Ultra-Low Latency

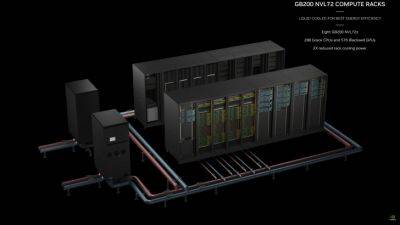

Conventional ways of joining thousands of accelerators include NVIDIA's NVLINK, the traditional Ethernet methods, and even AMD's very own Infinity Fabric. Still, they are confined in several ways, not just because of the interconnect efficiency they provide but also because of the lack of room for expansion, which has resulted in the industry finding alternates, one of which is Celestial AI's Photonic Fabric.

In an earlier post, we mentioned the importance of silicon photonics and how the technology, which combines laser and silicon technology, has become the next big thing in the world of interconnects. Celestial AI has leveraged it, harnessing the technology's powers to develop its Photonic Fabric solution.

According to the firm's co-founder Dave Lazovsky, the firm's Photonic Fabric has managed to gain massive interest among potential clients, not only receiving $175 million in the first round of funding but also receiving backing from the likes of AMD as well, which shows how big the interconnect method could turn out to be.

Moving on to the capabilities of Photonic Fabric, the firm has disclosed that the first generation of the technology can potentially provide 1.8 Tb/sec for every square millimeter, which the second iteration can see a whopping four times increment from its predecessor. However, due to the memory capacity limitations that come into